Research Article

# Active power compensation method for single-phase current source rectifier without extra active switches

ISSN 1755-4535 Received on 10th November 2015 Revised on 18th February 2016 Accepted on 2nd March 2016 doi: 10.1049/iet-pel.2015.0899 www.ietdl.org

Yonglu Liu, Yao Sun <sup>™</sup>, Mei Su

School of Information Science and Engineering, Central South University, Changsha, People's Republic of China

□ E-mail: yaosuncsu@gmail.com

Abstract: The existing active power decoupling methods for single-phase current source rectifiers (SCSRs) usually involve a lot of additional semiconductor devices or energy storage units, which is adverse to cost and efficiency. This study proposes an active power decoupling method to buffer the double-frequency ripple power. The main circuit is configured by adding only a decoupling capacitor and a diode to the traditional SCSR. Compared with the existing ones, the added components are minimised. The operating principle and modulation scheme are described. A closed-loop control method is developed to enhance twice the line frequency ripple power compensation performance. The guide for the selection of the decoupling capacitance is also discussed. Simulations and experimental results are presented to show the effectiveness of the method.

### 1 Introduction

With the development of power electronic technology, more and more applications involve single-phase power system. For example, in distributed power generation the energy which comes from photovoltaic (PV) panels, fuel cells or others is transferred to utility grid by single phase grid-connected inverters [1, 2]. The residential and industrial power supplies, electric vehicles with low power level [3], and lighting system [4] are powered by single-phase power system. However, the inherent ripple power at twice the line frequency [5] in single phase power converters introduces some side effects, which degrades system performance and decreases reliability [6–12].

To address the issue above, the solutions can be categorised into passive method and active method. The passive method results from the standpoints of hardware. It also includes two types: increasing the dc-link capacitance or inductance [13] and making use of the LC resonant filters [14–16]. They are easy to implement, but large volume and weight are undesirable from the perspectives of costs and power density.

The active method is based on the principle of buffering the ripple power with small capacitors/inductors, which allow large voltage/ current fluctuation. It can be further divided into two categories. One is implemented by swinging the dc-link bus voltage at twice the line frequency to buffer the ripple power [17–22]. It is usually carried out in two-stage single-phase inverters which consist of a front-end dc-dc converter and a downstream dc-ac inverter. The researches were mainly focused on maintaining the source current free from second ripple current [17-19] and dealing with the conflict between the dynamic response of dc-link voltage control and ac current quality [20, 21]. A distinct advantage of this method is that no extra circuit components are required. Its drawback consists in the limited applications (not suitable for single-stage power converters). In addition, since a second-order ripple voltage is superimposed on the dc bus, the voltage stress increases significantly, especially when the dc-link capacitance is small.

The other kind of active method is realised by adding an extra decoupling circuit. Recently this method has been extensively studied [23]. A variety of series and parallel compensation decoupling circuits [7, 24–32] are proposed to balance the power difference between the source and load. In the series compensation decoupling circuits [24, 25], the compensation voltage is injected to offset the pulsed voltage caused by the twice ripple power. In the parallel compensation decoupling circuits [7, 26–32] the compensation current is injected to prevent the pulsed current from

flowing into the dc-link capacitor. However, a common drawback of the active methods is that an additional switching circuit is required, which leads to higher cost and power losses. Therefore, active methods sharing switches partially [33–40] and even entirely [41–44] between the decoupling and original circuits are proposed. The shared switches can be a bridge arm [33–36, 41, 42, 45, 46] or two upper/lower switches [37, 38]. However, the penalties for reducing switches may be the reduced voltage utility ratio, increased switches voltage stress and the increased complexity in modulation and control [31, 45, 47].

The decoupling circuits for CSCs are investigated relatively less compared with those tailored for VSCs. Most of them [25, 36, 38, 40] still require two additional active switches and two diodes even if switch sharing is applied. The open-loop control in which the decoupling capacitor voltage reference is taken as control objective was usually adopted [25, 36, 40]. As a result, excellent decoupling performance is difficult to achieve due to various unknown disturbances, for example, parameter drifts and grid harmonics. In [48] the proposed active method for SCSR needs no extra switches. However, two identical decoupling capacitors are needed to buffer the ripple power and the modulation scheme is also complicated. Moreover, voltage stress of the semiconductor devices increases.

A decoupling solution for SCSR without requiring additional active switches is proposed in this paper. The decoupling circuit only needs a decoupling capacitor and a protection diode, which is half the cost of that in [48]. Compared with the existing ones, the proposed one has advantages in cost and size. Meanwhile, the modulation algorithm is also easy to implement. To remove ripple power in the dc-link inductor completely a closed-loop control method is used. The rest of the paper is organised as follows: Section 2 introduces the proposed circuit configuration and switching states. Section 3 discusses the modulation scheme and control strategy. The selection of the decoupling capacitance is discussed in Section 4. Simulations and experimental results are proved in Section 5. Finally, the conclusions are made in Section 6.

## 2 Circuit configuration and switching states

## 2.1 Circuit configuration

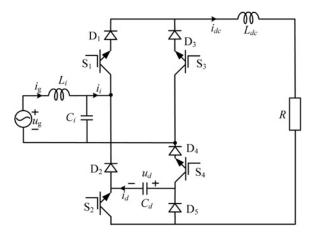

Fig. 1 shows the proposed power decoupling circuit. It is formed by adding a decoupling capacitor  $C_{\rm d}$  and a diode  $D_{\rm 5}$  into the conventional SCSR. The second ripple power is diverted to  $C_{\rm d}$  by

Fig. 1 Proposed power decoupling circuit

controlling switches  $S_2$  and  $S_4$  properly. Then the dc-link current  $i_{\rm dc}$  can be kept constant even if a small inductor  $L_{\rm dc}$  is used.

## 2.2 Switching states

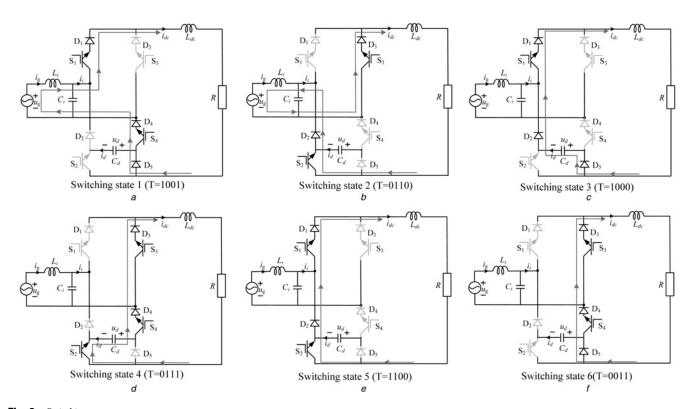

In Fig. 1,  $S_1$  and  $S_3$  are complementary, whereas  $S_2$  and  $S_4$  do not obey that constraint. Fig. 2 illustrates six switching states, which are used in this paper. In the figures,  $T = (S_1 \ S_2 \ S_3 \ S_4)$  denotes the states of the four active switches, where  $S_i$ = '1' (i=1, 2, 3, 4) indicates the corresponding switch is turned on and  $S_i$ = '0' turned off. The switching states are divided into three groups in terms of functions. The first group includes the switching states 1 and 2, in which the ac side is connected to the dc-link current loop and the decoupling capacitor  $C_d$  is bypassed. This group contributes to

synthesising the input current (transferring active power). The second group consists of switching states 3 and 4, in which the ac side is bypassed and the decoupling capacitor  $C_{\rm d}$  works. This group is exclusively used to synthesise the decoupling capacitor current (buffer the ripple power). The third group is composed of switching states 5 and 6, which provide a freewheeling path for the dc-link current  $i_{\rm dc}$ . The effects of different switching states on currents  $i_i$  and  $i_{\rm d}$  are summarised in Table 1. The expected currents  $i_i$  and  $i_{\rm d}$  can be synthesised by using the six switching states.

# 3 Modulation scheme and control strategy

## 3.1 Modulation scheme

To analyse the power flow of the proposed SCSR, the grid ac voltage  $u_g$  and current  $i_g$  are defined at first.

$$u_{\rm g} = V\cos(\omega t) \tag{1}$$

$$i_{\rm g} = I\cos\left(\omega t + \varphi\right) \tag{2}$$

where V and I are the amplitudes,  $\omega$  is the angular frequency, and  $\varphi$  is the displacement angle. Then, the instantaneous power  $p_{\rm ac}$  of the grid is expressed as

$$p_{\rm ac} = u_{\rm g}i_{\rm g} = \underbrace{\frac{VI\cos(\varphi)}{2}}_{\tilde{p}} + \underbrace{\frac{VI\cos(2\omega t + \varphi)}{2}}_{\tilde{p}}.$$

(3)

In most applications, the load consumes constant power  $\bar{P}$ . Hence, the ripple power  $\tilde{P}$  should be buffered by the decoupling capacitor  $C_{\rm d}$ . By ignoring the power losses, the decoupling capacitor voltage

Fig. 2 Switching states

- a Switches S<sub>1</sub> and S<sub>4</sub> are turned on, and switches S<sub>2</sub> and S<sub>3</sub> are turned off.

- b Switches  $S_2$  and  $S_3$  are turned on, and switches  $S_1$  and  $S_4$  are turned off.

- $\it c$  Switch  $S_1$  is turned on, and switches  $S_2$ ,  $S_3$ , and  $S_4$  are turned off.

- d Switches S<sub>2</sub>, S<sub>3</sub>, and S<sub>4</sub> are turned on, and switch S<sub>1</sub> is turned off.

- e Switches  $S_1$  and  $S_2$  are turned on, and switches  $S_3$  and  $S_4$  are turned off. f Switches  $S_3$  and  $S_4$  are turned on, and switches  $S_1$  and  $S_2$  are turned off.

Table 1 Switching states and currents

| Switching states | i <sub>i</sub> | i <sub>d</sub>                      |

|------------------|----------------|-------------------------------------|

| 1                | $i_{ m dc}$    | 0                                   |

| 2                | $-i_{dc}$      | 0                                   |

| 3                | 0              | i <sub>dc</sub>                     |

| 4                | 0              | l <sub>dc</sub><br>−i <sub>dc</sub> |

| 5,6              | 0              | 0                                   |

$u_{\rm d}$  and current  $i_{\rm d}$  can be expressed as [25]

$$u_{\rm d} = \sqrt{\bar{u}_{\rm d}^2 + \frac{VI\sin\left(2\omega t + \varphi\right)}{2\omega C_{\rm d}}} \tag{4}$$

$$i_{\rm d} = \frac{VI\cos(2\omega t + \varphi)/2}{\sqrt{\bar{u}_{\rm d}^2 + \left(VI\sin(2\omega t + \varphi)/2\omega C_{\rm d}\right)}}\tag{5}$$

where  $\bar{u}_{\rm d}$  is the dc component of  $u_{\rm d}$ . Assume that  $d_j$   $(j=1,\ 2,\ 3,\ 4,\ 5,\ 6)$  is the duty ratio of the switching state j, six duty ratios are subject to the following equation

$$\sum_{i=1}^{6} d_j = 1. (6)$$

Then,  $i_i$  and  $i_d$  can be expressed as

$$\begin{bmatrix} i_i \\ i_d \end{bmatrix} = \begin{bmatrix} d_1 - d_2 \\ d_3 - d_4 \end{bmatrix} \cdot i_{dc}. \tag{7}$$

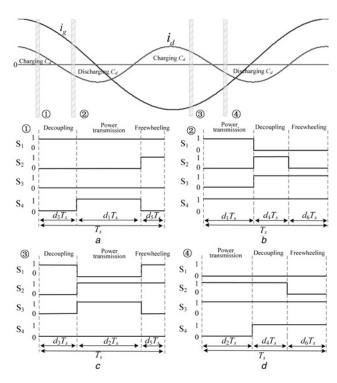

Fig. 3 Switching patterns

- a Charging  $C_d$  when ac current is positive

- b Discharging  $C_d$  when ac current is positive

- c Charging  $C_d$  when ac current is negative

- d Discharging  $C_{\rm d}$  when ac current is negative

Substitute (3), (5), and (6) into (7),  $d_i$  can be expressed as

$$\begin{cases} d_{1} = \begin{cases} i_{i\_ref}/i_{dc} & i_{i\_ref} > 0 \\ 0 & i_{i\_ref} \le 0 \end{cases} & d_{2} = \begin{cases} 0 & i_{i\_ref} > 0 \\ -i_{i\_ref}/i_{dc} & i_{i\_ref} \le 0 \end{cases} \\ d_{3} = \begin{cases} i_{d\_ref}/i_{dc} & i_{d\_ref} > 0 \\ 0 & i_{d\_ref} \le 0 \end{cases} & d_{4} = \begin{cases} 0 & i_{d\_ref} > 0 \\ -i_{d\_ref}/i_{dc} & i_{d\_ref} > 0 \end{cases} \\ d_{5} = \begin{cases} 1 - \sum_{j=1}^{4} d_{j} & i_{d\_ref} > 0 \\ 0 & i_{d\_ref} \le 0 \end{cases} & d_{6} = \begin{cases} 0 & i_{d\_ref} > 0 \\ 1 - \sum_{j=1}^{4} d_{j} & i_{d\_ref} \le 0 \end{cases} \end{cases}$$

where  $i_{i_{-}\mathrm{ref}}$  and  $i_{d_{-}\mathrm{ref}}$  are the references of the grid current and decoupling capacitor current, respectively. To reduce the dc-link current ripple, in each switching period  $T_{\rm s}$ , the decoupling operation is first carried out when charging  $C_d$ ; while the power transmission is prior when discharging  $C_d$ . To balance heat dissipation of each bridge, switching state 5/6 is carried out when charging/discharging  $C_d$ . Fig. 3 shows the switching patterns. From (8) and Fig. 3, it is easy for the modulation to be implemented in FPGA (CPLD).

#### 3.2 Control strategy

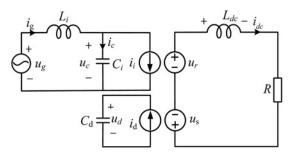

According to Fig. 1, the equivalent averaged circuit model of the proposed converter is illustrated in Fig. 4. The averaged voltages  $u_r$  and  $u_c$  are provided by filter capacitor voltage and decoupling capacitor voltage, respectively. Then the differential equations of the converter are obtained as follows

$$L_i \frac{\mathrm{d}i_\mathrm{g}}{\mathrm{d}t} = u_\mathrm{g} - u_\mathrm{c} \tag{9}$$

$$C_i \frac{\mathrm{d}u_{\rm c}}{\mathrm{d}t} = i_{\rm g} - i_i \tag{10}$$

$$L_{\rm dc} \frac{\mathrm{d}i_{\rm dc}}{\mathrm{d}t} = u_r - u_s - Ri_{\rm dc} \tag{11}$$

$$C_{\rm d} \frac{\mathrm{d}u_{\rm d}}{\mathrm{d}t} = i_{\rm d} \tag{12}$$

$$i_i = (d_1 - d_2)i_{dc} (13)$$

$$i_{\rm d} = (d_3 - d_4)i_{\rm dc} \tag{14}$$

$$u_r = \frac{i_i}{i_{dc}} u_c = (d_1 - d_2) u_c \tag{15}$$

$$u_s = \frac{i_d}{i_{dc}} u_d = (d_3 - d_4) u_d$$

(16)

where  $i_{\rm g},\ i_{

m dc},\ u_{

m d}$  are output variables;  $i_i$  and  $i_{

m d}$  are control input

The precise open-loop reference (the decoupling capacitor voltage  $u_{\rm d}$  or current  $i_{\rm d}$ ) for power decoupling is difficult to obtain due to

Fig. 4 Equivalent averaged circuit

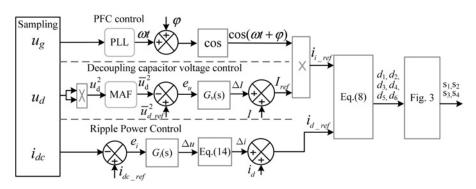

power losses and parameter perturbations. To achieve good decoupling performance a closed-control strategy in [48] is adopted. Its basic idea is that  $i_{\rm d}$  is responsive for regulating dc-link current  $i_{\rm dc}$  and  $i_i$  is in charge of PFC as well as maintaining the dc component of the  $u_{\rm d}$  at a given level.

3.2.1 Ripple power control: Actually, if the ripple power is not completely absorbed by the decoupling capacitor  $C_{\rm d}$ , the residual part will be imposed on the dc-link inductor  $L_{\rm dc}$ . Then the voltage-second balance will be broken and the dc-link current cannot be kept constant. Therefore, the error between the dc-link current reference and its detected value can be used to reflect the decoupling effect indirectly. As shown in Fig. 5, the error is sent to a proportional-integral (PI) controller. Then the reference  $i_{\rm d\_ref}$  can be obtained as follows

$$i_{\text{d\_ref}} = i_{\text{d}} + \frac{i_{\text{dc}}}{u_{\text{d}}} G_i(s) (i_{\text{dc\_ref}} - i_{\text{dc}})$$

(17)

where  $i_d$  serves as a forward compensation in the control to improve the dynamic response.

3.2.2 Decoupling capacitor voltage control: The decoupling capacitor voltage fluctuates as a result of buffering the ripple power. Though the required average ripple power through  $C_{\rm d}$  over a line frequency cycle is zero, the power losses due to switches and capacitors are unavoidable. Therefore, the dc component of the decoupling capacitor voltage should be maintained at a predetermined level. Before introducing the voltage control of  $C_{\rm d}$ , assume the dc-link current subsystem is in steady state.

According to (11) and (15),  $u_s$  in steady state can be expressed as

$$u_s = \frac{i_i}{i_{dc}} u_c - Ri_{dc}. \tag{18}$$

Substitute (15) and (18) to (12), the voltage dynamic of  $C_d$  is express as follows.

$$\frac{C_{\rm d}}{2} \frac{\mathrm{d}x}{\mathrm{d}t} = u_{\rm c} i_i - R i_{\rm dc}^2 \tag{19}$$

where  $x = u_{\rm d}^2$ . Clearly, the voltage across  $C_{\rm d}$  can be controlled by control input  $i_i$ . By ignoring the effects of the input filters,  $i_i \simeq i_{\rm g}$  and  $u_{\rm c} \simeq u_{\rm g}$ , then (19) can be rewritten as

$$\frac{C_{\rm d}}{2} \frac{\mathrm{d}x}{\mathrm{d}t} = \frac{VI}{2} \left[ \cos\left(\varphi\right) + \cos\left(2\omega t + \varphi\right) \right] - Rt_{\rm dc}^2. \tag{20}$$

Since (20) is a periodic system, the periodic averaging method [49] is used to design the controller. Then the average differential equation of (20) is

$C_{\rm d} \frac{\mathrm{d}\bar{x}}{\mathrm{d}t} = VI \cos(\varphi) - 2Ri_{\rm do}^2$

where  $\bar{x} = \bar{u}_d^2 = (1/T) \int_{t-T}^t x(\tau) d\tau$ , and  $\bar{x}$  is obtained by a moving average filter in implementation. Equation (21) is a simple first-order system, thus  $G_v(s)$  is achieved by a PI controller. Then the reference  $i_i$  ref can be written as

$$i_{i\_ref} = I_{\_ref} \cos(\omega t + \varphi)$$

$$= \left\{ I + G_{\nu}(s)(\bar{u}_{d\_ref}^2 - \bar{u}_{d}^2) \right\} \cos(\omega t + \varphi)$$

(22)

where  $I = 2\bar{P}/V$  is the feed-forward term to increase the dynamic response of the current control.

Fig. 5 shows the overall block diagram of the control scheme. It mainly includes a phase locking loop, a voltage controller and a current controller. Compared with the control scheme in [25], the complexity does not increase a lot. A highlight merit of the proposed control is the feed-back regulation of the dc-link current, which enhances the decoupling effects.

## 4 Design of the decoupling circuit

In this section, the values of  $\bar{u}_{\rm d}$  and  $C_{\rm d}$  will be determined. There are two basic constraints imposed by the normal operation of the converter. One is that the decoupling capacitor voltage should be higher than the grid voltage. Then, the misgating-on of  $D_2$  can be avoided when carrying out switching states 1 and 4. The other is that the synthesis of input current and decoupling current should be accomplished in each switching period, that is,  $\sum_{j=1}^4 d_j$  should be no more than unity. Hence, inequalities (23) and (24) should hold for any time

$$\sqrt{\bar{u}_{\rm d}^2 + \frac{VI\sin(2\omega t + \varphi)}{2\omega C_{\rm d}}} \ge |V\cos(\omega t)|$$

(23)

$$m(\left|\cos\left(\omega t + \varphi\right)\right| + \left|\frac{V\cos\left(2\omega t + \varphi\right)/2}{\sqrt{\bar{u}_{d}^{2} + \left(VI\sin\left(2\omega t + \varphi\right)/2\omega C_{d}\right)}}\right|) \le 1 \quad (24)$$

where  $m = I/i_{dc}$  is the modulation index.

Assume that the converter works in unity power factor, the maximum grid current is  $I_{\rm m}$ , and the required maximum modulation index is M.

On the basis of the assumptions above, (23) can be simplified as

$$\bar{u}_{\rm d} \ge \sqrt{\frac{1}{2} \left( V^2 + \sqrt{V^4 + \left(\frac{VI_{\rm m}}{\omega C_{\rm d}}\right)^2} \right)} \tag{25}$$

Equation (24) can also be simplified as

$$M \le \frac{1}{1 + \left(V/2\sqrt{\bar{u}_{\rm d}^2 - \left(VI_{\rm m}/2\omega C_{\rm d}\right)}\right)} \tag{26}$$

(21)

Fig. 5 Block diagram of the control scheme

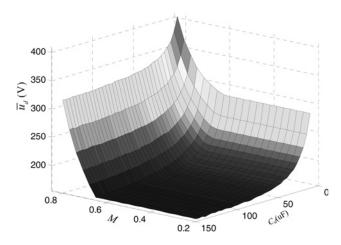

Fig. 6 Decoupling capacitor voltage as a function of the decoupling capacitance and modulation index

Table 2 Parameters used in analysis, simulation, and experiment

| Parameters               | Symbols          | Values       |

|--------------------------|------------------|--------------|

| input phase voltage      | V                | 110√2V       |

| source angular frequency | ω                | 314 rad/s    |

| input filters            | $L_i/C_i$        | 0.6 mH/20 μF |

| Dc filter inductor       | $L_{dc}$         | 5 mH         |

| active buffer capacitor  | $C_{d}$          | 90 μF        |

| load resistance          | R<br>P           | 8.7 Ω        |

| load power               | P                | 217.5 W      |

| switching frequency      | $f_{\mathtt{s}}$ | 20 kHz       |

Besides the constraints imposed by its normal operation, the maximum voltage stress on switches should be considered. Therefore,

$$\max(u_{\rm d}) \le u_{\rm p} \tag{27}$$

where  $u_{\rm p}$  denotes the maximum permissible voltage, (27) can be

Fig. 7 Simulation results

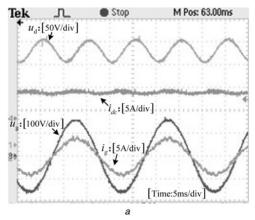

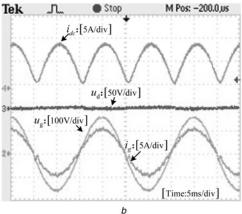

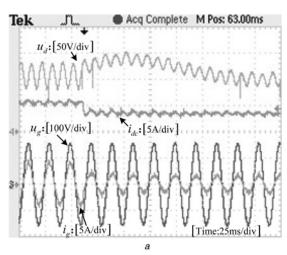

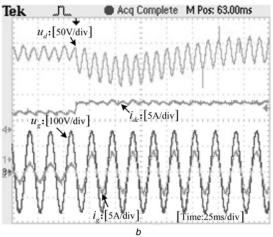

Fig. 8 Steady-state experimental waveforms

- a With decoupling function

- b Without decoupling function

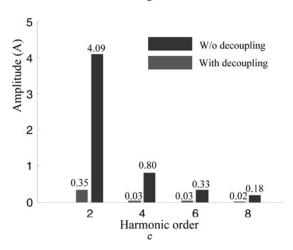

- c Spectral analysis for dc-link current

rewritten as

$$\sqrt{\bar{u}_{\rm d}^2 + \frac{VI_{\rm m}}{2\omega C_{\rm d}}} \le u_{\rm p} \tag{28}$$

On the basis of inequalities (25), (26) and (28), a feasible region for  $\bar{u}_{\rm d}$  and  $C_{\rm d}$  can be solved. Using the parameters in simulation and experiments, the relation between  $\bar{u}_{\rm d}$ ,  $C_{\rm d}$ , and M is shown in Fig. 6. As can be seen, when M is small,  $\bar{u}_{\rm d}$  is not affected by M. Because (25) is the dominant constraint. However, when M is large, (26) becomes the dominant constraint. Therefore,  $\bar{u}_{\rm d}$  increases significantly with increasing M. On the other hand, increasing capacitance obviously can decrease  $\bar{u}_{\rm d}$ . However, once  $C_{\rm d}$  is beyond a certain value, increasing capacitance cannot

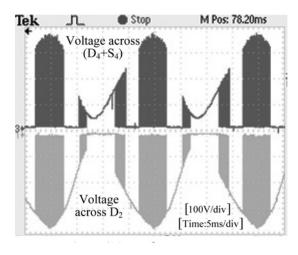

**Fig. 9** Experimental waveforms of voltages across  $(D_4 + S_4)$  and  $D_2$

decrease  $\bar{u}_d$  significantly. In this study, by making a trade-off between voltage stress and cost the decoupling capacitance is 90  $\mu F$  and  $\bar{u}_d$  is set to 200 V.

# 5 Simulations and experimental results

Simulation study is carried out in Matlab/Simulink environment and the circuit parameters are listed in Table 2. The waveforms in steady-state and transient operation are presented in Fig. 7. At

**Fig. 10** Dynamic experimental waveforms a 100% to 40% step-down load change b 40% to 100% step-up load change

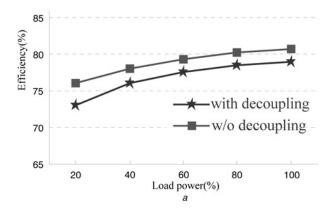

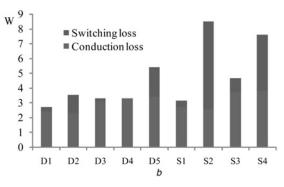

Fig. 11 Power losses analysis

a Efficiency comparison

b Loss distribution of the proposed converter with 100% load operation

beginning system operates in steady-state with a 5.4 A dc-link current. The step-down change of dc-link reference from 5.4 to 3.4 A and step-up change from 3.4 to 5.4 A happen at t = 0.36 and 0.5 s. As can be seen, the dc-link current  $i_{\rm dc}$  is always smooth in both operation states because the ripple power is diverted to the decoupling capacitor  $C_{\rm d}$ . Meanwhile, the low dc-link current ripple verifies the effectiveness of the designed switching patterns. The source current  $i_{\rm g}$  is always sine shaped and in phase with the source voltage  $u_{\rm g}$ .

A prototype was built to verify the feasibility of the decoupling topology and control schemes. The control algorithm of the converter is realised by a combination of digital signal processor TMS320F28335 and field programmable gate array FPGA EP2C8T144C8N. The decoupling capacitor is formed by connecting three  $30 \,\mu\text{F}/490 \,\text{V}$  film capacitors in parallel. Fig. 8ashows the steady-state experimental waveforms. As can be seen, the experimental results are in good agreement with the simulation results. The THD of source current  $i_{\rm g}$  is 4.63%, which meets the requirements of standard IEC/EN 61000-3-2 Class A. After disabling the decoupling function the twice ripple power will be imposed on the dc-link inductor immediately and the related experimental waveforms are shown in Fig. 8b. Clearly, the dc-link current fluctuates with twice the line frequency. The grid ac current is seriously distorted at the valley of the dc-link current. Fig. 8c shows the spectrum of the dc-link current with and without decoupling. It is clear that there is a dramatic reduction of the second harmonic current when activating decoupling function. Other low-frequency harmonic components are also reduced.

Fig. 9 shows the waveforms of voltages across  $(D_4 + S_4)$  and  $D_2$ . As seen, the envelope of the voltage across  $(D_4 + S_4)$  is  $(u_g + u_d)$ , which is always positive. Therefore, the reverse voltage across  $D_4$  is negative during the turn-off process, which reduces the turn-off loss. The envelope of the voltage across  $D_2$  is  $(-u_g - u_d)$ , which is always negative. Then  $D_2$  can be blocked reliably when  $S_4$  is in the on state. On the other hand, the voltage stress of  $S_4$  and  $S_4$  are the highest in all the semiconductor devices.

Fig. 10 shows the dynamic response of the system when the load power is subject to a 100% to 40% step-down change and a 40% to

100% step-up change. As can be seen, in Fig. 10a the dc-link current  $i_{\rm dc}$  decreases from 5.4 to 3.4 A quickly due to the closed-loop control method. The excess energy in the dc-link inductor is transferred to the decoupling capacitor and the capacitor voltage level is raised. The decoupling capacitor voltage enters steady state relatively slow as results of low bandwidth of the voltage control loop. With the decrease of the load power, the ripple power is reduced and the fluctuation range of  $u_{\rm d}$  decreases accordingly. Fig. 10b shows the opposite transient process. The experimental results also coincide with those in the simulation.

Fig. 11a illustrates the efficiency curves of the proposed converter and the conventional SCSR. As can be seen, the efficiency of the proposed converter is slightly lower than that of the conventional case. The main reason is the increased voltage stresses, which increases the switching power losses. As well known, all the active decoupling methods cause extra power losses. As reported in [6, 44], usually the efficiency penalty is more than two percentage points. However, in the proposed method the system efficiency drop under rated load power is 1.5%, which is lower than those reported in [25, 48]. Fig. 11b shows the estimated power loss distribution. Apparently, the switching losses of the semiconductor devices in the lower bridge arm are significant. As analysed previously, switching loss does not happen to  $D_4$  because the reverse voltage across  $D_4$  is negative.

# 6 Conclusion

An active ripple power decoupling method is proposed for SCSR to reduce the twice ripple power and the dc-link inductance. A highlight merit of the method is that the required extra components are minimised, which reduces cost and improves reliability. The operating principle has been analysed and a closed-loop control method is used to enhance the ripple power decoupling effects. Simulations and experimental results in both steady-state and transient operations are obtained. The results show that the proposed decoupling method reduces the second harmonic current by 91.4%, which reduces required dc-link inductance greatly. One shortcoming of the method is the increased switching voltage stress, which decreases the system efficiency inevitably. Thus, the efficiency optimisation will be studied in the future work.

## 7 Acknowledgments

This work was supported by the National Natural Science Foundation of China under Grant No. 61573382, the National High tech R&D Program of China under Grant 2015AA050604, the Project of Innovation-driven Plan in Central South University and Hunan Provincial Innovation Foundation for Postgraduate.

## 8 References

- 1 Singh, B., Singh, B.N., Chandra, A., et al.: 'A review of single-phase improved power quality AC-DC converters', *IEEE Trans. Ind. Electron.*, 2003, 50, (5), pp. 962–981

- 2 Cha, W.-J., Kim, K.-T., Cho, Y.-W., et al.: 'Evaluation and analysis of transformerless photovoltaic inverter topology for efficiency improvement and reduction of leakage current', *IET Power Electron.*, 2015, 8, (2), pp. 255–267

- 3 Yilmaz, M., Krein, P.: 'Review of battery charger topologies, charging power levels, infrastructure for plug-in electric and hybrid vehicles', *IEEE Trans. Power Electron.*, 2013, 28, (5), pp. 2151–2169

- Power Electron., 2013, 28, (5), pp. 2151–2169

Li, S., Tan, S.C., Lee, C., et al.: 'A survey, classification and critical review of light-emitting diode drivers', IEEE Trans. Power Electron., 2016, 31, (2), pp. 1503–1516

- 5 Wang, R., Wang, F., Boroyevich, D., et al.: 'A high power density single-phase PWM rectifier with active ripple energy storage', *IEEE Trans. Power Electron.*, 2011, 26, (5), pp. 1430–1443

- 6 Hu, H., Harb, S., Kutkut, N., et al.: 'A review of power decoupling techniques for microinverters with three different decoupling capacitor locations in PV systems', IEEE Trans. Power Electron., 2013, 28, (6), pp. 2711–2726

- IEEE Trans. Power Electron., 2013, 28, (6), pp. 2711–2726

Krein, P.T., Balog, R.S., Mirjafari, M.: 'Minimum energy and capacitance requirements for single-phase inverters and rectifiers using a ripple port', IEEE Trans. Power Electron., 2012, 27, (11), pp. 4690–4698

- 8 Chen, W., Hui, S.Y.R.: 'Elimination of an electrolytic capacitor in AC/DC light-emitting diode (LED) driver with high input power factor and constant output current', *IEEE Trans. Power Electron.*, 2012, 27, (3), pp. 1598–1607

- 9 Kim, H., Shin, K.G.: 'DESA: dependable, efficient, scalable architecture for management of large-scale batteries', *IEEE Trans. Ind. Inf.*, 2012, 8, (2), pp. 406–417

- 10 Lacressonniere, F., Cassoret, B., Brudny, J.F.: 'Influence of a charging current with a sinusoidal perturbation on the performance of a lead-acid battery', *IEE Electr. Power Appl.*, 2005, 152, (5), pp. 1365–1370

- 11 Fontes, G., Turpin, C., Astier, S., et al.: 'Interactions between fuel cells and power converters: influence of current harmonics on a fuel cell stack', *IEEE Trans. Power Electron*, 2007, 22, (2), pp. 670–678

- Gemmen, R.S.: 'Analysis for the effect of inverter ripple current on fuel cell operating condition', *J. Fluids Eng.*, 2003, 125, (3), pp. 576–585

Dahler, P., Knapp, G., Nold, A.: 'New generation of compact low voltage IGBT

- 13 Dahler, P., Knapp, G., Nold, A.: 'New generation of compact low voltage IGBT converter for traction applications'. Proc. IEEE European Conf. Power Electronics, Dresden, September 2005, pp. 9–18

- 14 Vasiladiotis, M., Rufer, A.: 'Dynamic analysis and state feedback voltage control of single-phase active rectifiers with DC-link resonant filters', *IEEE Trans. Power Electron*, 2014, 29, (10), pp. 5620–5633

- 15 Lo, Y.W., King, R.J.: 'High performance ripple feedback for the buck unity-power-factor rectifier', *IEEE Trans. Power Electron.*, 1995, **10**, (2), pp. 158–163

- 16 Hwu, K.-I., Tu, W.-C., Lai, C.-Y.: 'Light-emitting diode driver with low-frequency ripple suppressed and dimming efficiency improved', *IET Power Electron.*, 2014, 7, (1), pp. 105–113

- 17 Ksiazek, P.F., Ordonez, M.: 'Swinging bus technique for ripple current elimination in fuel cell power conversion', *IEEE Trans. Power Electron.*, 2014, 29, (1), pp. 170–178

- 18 Liu, X., Li, H., Wang, Z.: 'A fuel cell power conditioning system with low-frequency ripple-free input current using a control-oriented power pulsation decoupling strategy', *IEEE Trans. Power Electron.*, 2014, 29, (1), pp. 159–169

- 19 Kwon, J.M., Kim, E.H., Kwon, B.H., et al.: 'High-Efficiency fuel cell power conditioning system with input current ripple reduction', *IEEE Trans. Ind. Electron.*, 2009, 56, (3), pp. 826–834

- Electron., 2009, 56, (3), pp. 826–834

Galvez, J.M., Ordonez, M.: 'Swinging bus operation of inverters for fuel cell applications with small dc-link capacitance', *IEEE Trans. Power Electron.*, 2015, 30, (2), pp. 1064–1075

- 21 Levron, Y., Canaday, S., Erickson, R.: 'Bus voltage control with zero distortion and high bandwidth for single phase solar inverters', *IEEE Trans. Power Electron.*, 2016, 31, (1), pp. 258–269

- 22 Hu, Y., Du, Y., Xiao, W., et al.: 'DC-link voltage control strategy for reducing capacitance and total harmonic distortion in single-phase grid-connected photovoltaic inverters', IET Power Electron., 2015, 8, (8), pp. 1386–1393

- 23 Sun, Y., Liu, Y., Su, M., et al.: 'Review of active power decoupling topologies in single-phase systems', IEEE Trans. Power Electron., 2016, 31, (7), pp. 4778–4794

- 24 Wang, H., Chung, H.S.H., Liu, W.: 'Use of a series voltage compensator for reduction of the DC-link capacitance in a capacitor-supported system', *IEEE Trans. Power Electron.*, 2014, 29, (3), pp. 1163–1175

- Trans. Power Electron., 2014, 29, (3), pp. 1163–1175

Han, H., Liu, Y., Sun, Y., et al.: 'Single-phase current source converter with power decoupling capability using a series-connected active buffer', *IET Power Electron.*, 2015, 8, (5), pp. 700–707

- 26 Harb, S., Mirjafari, M., Balog, R.S.: 'Ripple-port module-integrated inverter for grid-connected PV applications', *IEEE Trans. Ind. Appl.*, 2013, 49, (6), pp. 2692–2698

- 27 Larsson, T., Ostlund, S.: 'Active DC link filter for two frequency electric locomotives'. Proc. Electr. Railways United Eur. Conf, Amsterdam, March 1995, pp. 97–100

- Jang, M., Ciobotaru, M., Agelidis, V.G.: 'A single-stage fuel cell energy system based on a buck--boost inverter with a backup energy storage unit', *IEEE Trans. Power Electron.*, 2012, 27, (6), pp. 2825–2834

Cai, W., Liu, B., Duan, S., et al.: 'An active low-frequency ripple control method

- 29 Cai, W., Liu, B., Duan, S., et al.: 'An active low-frequency ripple control method based on the virtual capacitor concept for BIPV systems', *IEEE Trans. Power Electron.*, 2014, 29, (4), pp. 1733–1745

- 30 Yang, Y., Ruan, X., Zhang, L., et al.: 'Feed-forward scheme for an electrolytic capacitor-less AC/DC LED driver to reduce output current ripple', IEEE Trans. Power Electron., 2014, 29, (10), pp. 5508–5517

- 31 Cao, X., Zhong, Q., Ming, W.: 'Ripple eliminator to smooth DC-Bus voltage and reduce the total capacitance require', *IEEE Trans. Ind. Electron.*, 2015, 62, (4), pp. 2224–2235

- 32 Mahadeva Iyer, V., John, V.: 'Low-frequency dc bus ripple cancellation in single phase pulse-width modulation inverters', *IET Power Electron.*, 2015, 8, (4), pp. 497–506

- 33 Li, H., Zhang, K., Zhao, H., et al.: 'Active power decoupling for high-power single-phase PWM rectifiers', IEEE Trans. Power Electron., 2013, 28, (3), pp. 1308–1319

- 34 Su, M., Pan, P., Long, X., et al.: 'An active power-decoupling method for single-phase AC-DC converters', *IEEE Trans. Ind. Inf.*, 2014, 10, (1), pp. 461–468

- 35 Shimizu, T., Jin, Y., Kimura, G.: 'DC ripple current reduction on a single-phase PWM voltage-source rectifier', IEEE Trans. Ind. Appl., 2000, 36, (4), pp. 1419–1429

- 6 Bush, C.R., Wang, B.: 'A single-phase current source solar inverter with reduced-size DC link'. Proc. IEEE ECCE, San Jose, CA, September 2009, pp. 54–59

- Fan, S., Xue, Y., Zhang, K.: 'Novel active power decoupling method for single-phase photovoltaic or energy storage applications'. Proc. IEEE ECCE, Raleigh, NC, September 2012, pp. 2439–2446

Vitorino, M.A., Hartmann, L.V., Fernandes, D.A., et al.: 'Single-phase current

- 58 Vitorino, M.A., Hartmann, L.V., Fernandes, D.A., et al.: 'Single-phase current source converter with new modulation approach and power decoupling'. Proc. IEEE APEC, Fort Worth, TX, March 2014, pp. 2200–2207

- 39 Shimizu, T., Fujita, T., Kimura, G., et al.: 'A unity power factor PWM rectifier with DC ripple compensation', IEEE Trans. Ind. Electron., 1997, 44, (4), pp. 447–455

- 40 Vitorino, M.A., Correa, M.B.R., Jacobina, C.B.: 'Single-phase power compensation in a current source converter'. Proc. IEEE ECCE, Denver, CO, September 2013, pp. 5288–5293

- 41 Qi, W., Wang, H., Tan, X., et al.: 'A novel active power decoupling single-phase PWM rectifier topology'. Proc. IEEE APEC, Fort Worth, TX, March 2014, pp. 89–95

- 42 Tang, Y., Blaabjerg, F.: 'A component-minimized single-phase active power decoupling circuit with reduced current stress to semiconductor switches', IEEE

- Trans. Power Electron., 2015, 30, (6), pp. 2905–2910

Zhu, G.R., Tan, S.C., Chen, Y., et al.: 'Mitigation of low-frequency current ripple in fuel-cell inverter systems through waveform control', IEEE Trans. Power Electron., 2013, 28, (2), pp. 779–792

- Serban, I.: 'Power decoupling method for single-phase h-bridge inverters with no

- additional power electronics', *IEEE Trans. Ind. Electron.*, 2015, **62**, (8), pp. 4805–4813 Cai, W., Jiang, L., Liu, B., *et al.*: 'A power decoupling method based on four-switch three-port DC/DC/AC converter in DC microgrid', *IEEE Trans. Ind.* Appl., 2015, **51**, (1), pp. 336–343

- 46 Ming, W., Zhong, Q., Zhang, X.: 'A single-phase four-switch rectifier with significantly reduced capacitance', IEEE Trans. Power Electron., 2016, 31, (2), pp. 1618–1632

- Itoh, V-J-I., Fayashi, F.: 'Ripple current reduction of a fuel cell or a single-phase isolated converter using a dc active filter with a center tap', *IEEE Trans. Power Electron.*, 2010, **25**, (3), pp. 550–556

- Sun, Y., Liu, Y., Su, M., *et al.*: 'Active power decoupling method for single-phase current source rectifier with no additional active switches', IEEE Trans. Power Electron., 2016, 31, (8), pp. 5644–5654

- Sanders, J.A., Verhulst, F., Murdock, J.: 'Averaging methods in nonlinear dynamical systems' (Springer, New York, 2007, 2nd edn.)